# **USERS MANUAL**

# SIA-2322 SERIAL INTERFACE ADAPTER

Accessory for the

**Audio Precision System Two**

October 1996

Version 5.0

PN 8211.0021

Users Manual SIA-2322 Serial Interface Adapter

Copyright 1991, 1994, 1996 by Audio Precision, Inc.

Audio Precision P.O. Box 2209 Beaverton, Oregon 97075 U.S.A. Telephone (503) 627-0832 US Toll-free 1-800-231-7350 FAX (503) 641-8906

# **Table of Contents**

| 1. Th  | ne SIA-2322 Serial Interface Adapter               | . 1  |

|--------|----------------------------------------------------|------|

|        | 1.1. Connecting the SIA to System Two              | . 1  |

| 2. Se  | erial I/O Primer                                   | . 2  |

|        | 2.1. Purpose of this Section                       | . 2  |

|        | 2.2. Data Communication Interfaces                 | . 2  |

|        | 2.2.1. Serial and Parallel I/O Compared            | . 3  |

|        | 2.3. The Serial Data Frame                         | . 4  |

|        | 2.3.1. Word-Clock Pulse Width                      | . 4  |

|        | 2.3.2. Word-Clock Position                         | . 5  |

|        | 2.3.3. Data Framing Control                        | . 6  |

|        | 2.3.4. Data, Word-Clock, and Bit-Clock Polarity    | . 7  |

|        | 2.4. Serial Clocking Methods                       | . 8  |

| 3. Int | terfacing the SIA-2322 to the Target System        | . 10 |

|        | 3.1. Transmitter Interfacing to the Target System  | . 10 |

|        | 3.2. Transmitter Configuration Switches            | . 11 |

|        | 3.2.1. Serial Word Length Selection                | . 11 |

|        | 3.2.2. Serial Data Length Selection                | . 11 |

|        | 3.2.3. Serial Word Clock Position Selection        | . 12 |

|        | 3.2.4. Serial Framing and Clocking Control         | . 12 |

|        | 3.2.5. Serial Framing Examples                     | . 15 |

|        | 3.3. Receiver Interfacing to the Target System     | . 16 |

|        | 3.4. Receiver Configuration Switches               | . 18 |

|        | 3.4.1. Serial Word Length Selection                | . 18 |

|        | 3.4.2. Serial Data Length Selection                | . 18 |

|        | 3.4.3. Serial Word Clock Position Selection        | . 18 |

|        | 3.4.4. Serial Framing and Clocking Control         | . 19 |

|        | 3.5. System Performance Issues                     | . 22 |

|        | 3.6. Transmitter and Receiver N x FS Clock Control | . 23 |

| 4. Se  | erial Interface Timing                             | . 24 |

|        | 4.1. Transmitter I/O Timing                        | . 24 |

|        | 4.2. Receiver I/O Timing                           | . 25 |

| 5. | SIA-DUT Interfacing Examples                                                      | . 26 |

|----|-----------------------------------------------------------------------------------|------|

|    | 5.1. Configuring the SIA for Local Loopback                                       | . 26 |

|    | 5.2. Connecting the SIA Receiver to the Crystal CDB5336 Evaluation Board          | . 27 |

|    | 5.2.1. The Crystal CDB5336 in Slave Mode                                          | . 27 |

|    | 5.2.2. The Crystal CDB5336 in Master Mode                                         | . 28 |

|    | 5.3. Connecting the SIA Receiver to the Analog Devices AD1879<br>Evaluation Board | . 31 |

|    | 5.4. Connecting the SIA Transmitter to the Signetics TDA1541                      | . 33 |

# 1. The SIA-2322 Serial Interface Adapter

The Serial Interface Adapter (SIA) provides a means of interfacing the System Two Audio Measurement System to a variety of data acquisition, reconstruction and communication hardware that utilize a serial bus for the exchange of data. The SIA greatly increases System Two's flexibility in interfacing to serial systems for a wide range of tests and measurements.

The SIA consists of a parallel-to-serial transmitter and a serial-to-parallel receiver, each completely independent of the other. Since few serial communication standards exist, flexibility and ease of use were of primary concern in the design of the SIA. Some of the primary features provided by the SIA are:

- Serial word length support of 8 to 32 bits, one or two channels (time multiplexed);

- System Two data word length support of 8 to 24 bits, with optional 0 or 1 padding, LSB or MSB extension;

- □ Left- or right-justified data within the serial data frame;

- Data transmission and reception independently selectable as LSB- or MSB-first;

- Independently programmable word clock transition timing within the data frame, with bitwide and word-wide clock widths;

- □ Independently programmable bit and word clock sources (internal or external);

- □ TTL and CMOS logic level support on all inputs and outputs;

- □ Logic polarity control of data, word clocks and bit clocks.

#### 1.1. Connecting the SIA-2322 to System Two

The SIA exchanges data and derives its power through the System Two Dual Domain parallel ports. Two keyed 50-pin shielded cables are provided with the SIA-2322, and should be used for the connection between System Two and the SIA. Two BNC cables are also needed: one connects between System Two **MASTER CLOCK OUTPUT** and the corresponding BNC connector on the SIA; the other connects between System Two **TRANSMIT FRAME SYNC** and the corresponding BNC connector on the SIA. Prior to connecting the SIA to System Two, be sure that power to System Two is turned off. The connectors are keyed to prevent incorrect installation of the cables. Note the location of the connector keys before attempting to install the cables. Install the two cables between the System Two parallel input/output ports and the corresponding ports on the rear panel of the SIA. If after installation the SIA does not appear to be operating, press the SIA reset switch located on the rear panel of the SIA.

# 2. Serial I/O Primer

# 2.1. Purpose of this Section

The following section presents a brief overview of serial I/O interfaces and the various parameters that are used, and is intended for those who are unfamiliar with serial communication techniques and their technical issues. In this section, the two principal data communication interfaces used in the digital audio world are identified, and their strengths and weaknesses are compared. An in-depth description of the serial data frame is provided, followed by a discussion of common serial clocking configurations.

# 2.2. Data Communication Interfaces

It is often desirable to exchange digital information between two or more systems -- for example, between System Two and a digital to analog converter (DAC). To facilitate data transfer between systems, an electrical interface is required. There are two principal interfaces used for exchanging data between systems: the *serial* interface and the *parallel* interface.

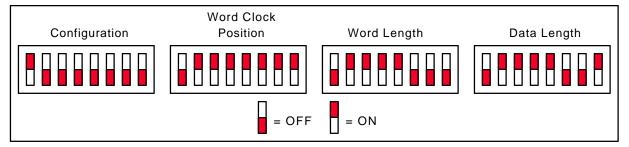

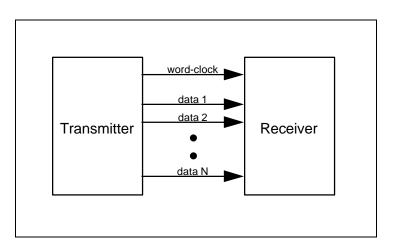

A serial interface usually has three primary electrical connections between the communicating systems: 1) a bit-clock line, 2) a word-clock (or word-strobe) line, and 3) a data line (see figure 1). A *data word*, or group of bits, is transmitted from a *data source* to a *data sink* in a bit-by-bit sequence (that is, serially) over the three-wire interface. Some communicating systems that require the exchange of data in both directions utilize a serial interface that includes two such sets of electrical connections, one for each direction. Such an interface allows the simultaneous exchange of data in both directions. Yet another bi-directional serial data interface utilizes only one set of electrical connections between two or more systems. Known as I<sup>2</sup>S, this interface allows the exchange of data between a number of interconnected systems using a common serial *bus*<sup>1</sup>. Only two systems at a time may communicate on an I<sup>2</sup>S serial bus. The SIA-2322 supports all of the above serial communication interfaces.

Figure 1. Typical serial interface configuration.

A parallel interface usually has two primary electrical connections between the communicating systems: 1) a word-clock line, and 2) two or more data lines (see figure 2). A data word is transmitted from the source to the destination one word at a time. The SIA-2322

<sup>&</sup>lt;sup>1</sup> The I<sup>2</sup>S, or *Inter-IC Sound*, bus interface was developed by Signetics Company.

does not support parallel communication interfaces; however, the System Two Digital I/O (DIO) option does support parallel communication interfaces with data word widths of up to 24 bits.

Figure 2. Typical parallel interface configuration.

# 2.2.1. Serial and Parallel I/O Compared

Serial and parallel interfaces each have unique advantages and disadvantages (see Table 1). The most obvious advantage of serial I/O over parallel I/O is the number of electrical connections that are required to facilitate communication between two systems. Data communication over a serial interface can be accomplished with as few as three connections -- regardless of data word size. A parallel interface requires at least N + 1 connections (where N is the word size in bits). Because of this, the cost of interconnect hardware is generally lower for serial I/O than for parallel I/O. Serial interfaces also tend to be more flexible than parallel interfaces because the data word size for a serial interface is user definable, while the data word size for a parallel interface is dictated by the number of interconnects between the communicating systems.

| Evaluation Criteria                    | Serial       | Parallel |

|----------------------------------------|--------------|----------|

| Reduced interconnect hardware and cost | $\checkmark$ |          |

| Maximum flexibility of data word size  | 1            |          |

| Highest data throughput                |              | 1        |

| Simplicity of interface logic          |              | 1        |

Table 1. Comparison of serial and parallel interfaces

Parallel interfaces have two significant advantages of their own. Since a serial interface must transmit one bit of data per bit-clock time, it takes N bit-clock periods to transmit a data word of size N bits (that is, there are N bit-clock periods per word-clock period). A parallel interface can transmit N bits in a single word-clock period -- therefore, a parallel interface can transmit N times more data than a serial interface in one clock period (it is assumed that the parallel word-clock period is equal to the serial bit-clock period). For example, if a 16-bit parallel interface has a word-clock period of 48 kHz, it can transfer 768 thousand bits of data per second (768 kbps). A comparable serial interface with a 48 kHz bit-clock can transfer only 48 thousand bits of data per second. To achieve the 768 kbps transfer rate, the serial interface would have to

use a bit-clock period of 768 kHz. The lower clock rate for a given data throughput is a major advantage of parallel interfaces over serial interfaces. Additionally, the design circuitry necessary to implement a parallel interface tends to be simpler than that required to implement a serial interface.

Traditionally, parallel interfaces were the preferred digital interface between communicating systems. Serial I/O, however, has rapidly grown to become the dominant interface for the exchange of information between two audio systems. This has been fueled by advances in semiconductor speed and cost reduction, and by the desire to minimize interconnect hardware between communicating systems.

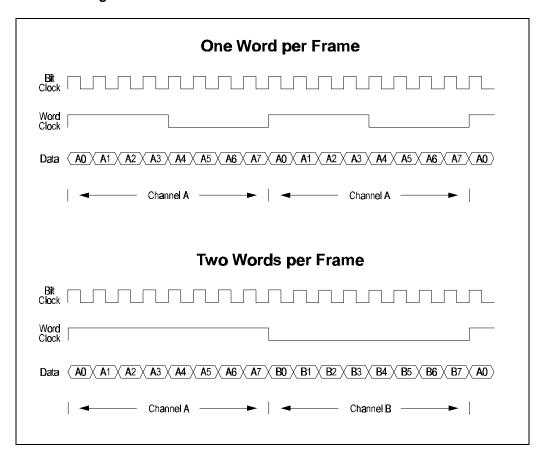

#### 2.3. The Serial Data Frame

Data that is transmitted over a serial interface is usually grouped in *frames*. A serial data frame is a grouping of one or more consecutive data words. The most common frame sizes are one (single channel or mono) and two (dual channel or stereo) data words per frame (see figure 3). There are four principal parameters that affect how data is transmitted within a data frame: the word-clock pulse width, the position of word-clock logic transitions relative to the data, data framing control, and word- and bit-clock polarity.

#### Figure 3. One- and two-channel serial data frame formats.

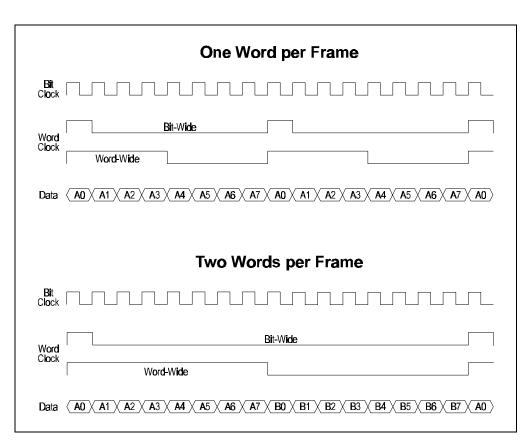

# 2.3.1. Word-Clock Pulse Width

The pulse width of the word-clock signal is usually either one bit-clock in duration (that is, the word-clock is *bit-wide*), or N bit-clocks in duration (the word-clock is *word-wide*), where N is the number of bits per word. As shown in figure 4, the *leading edge* of a clock pulse usually delineates the start of the data frame.

#### 2.3.2. Word-Clock Position

While the edge of the word-clock pulse is used to delineate the start of the data frame, the location of the first data bit within the frame can vary (see figure 5). The location of the data relative to the start of the data frame is termed the *word-clock position*<sup>2</sup>. The word-clock position within a data frame can vary from zero to N-1, where position zero corresponds to the *first* bit position of the first word, and position N-1 corresponds to the *last* bit position of the first word in the frame. The word-clock position for a given interface depends upon the requirements of the communicating systems. For example, the I<sup>2</sup>S bus standard dictates that the word-clock position be N-1. Most communicating systems utilize a word-clock position of zero or one.

Perhaps more appropriately, the word-clock position can be thought of as the location of word-clock relative to the start of the data frame. Either interpretation yields the same result -- the first data bit and the word-clock pulse can differ in position.

|                  | One Word per Frame                                                                                                                                                                                                                                                                         |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit<br>Clock     |                                                                                                                                                                                                                                                                                            |

|                  | WC Position = 0                                                                                                                                                                                                                                                                            |

| Word             | WC Position = 1                                                                                                                                                                                                                                                                            |

|                  | WC Position = 7                                                                                                                                                                                                                                                                            |

| Data AO A1 X     | $ \hline \textbf{A2} \land \textbf{A3} \land \textbf{A4} \land \textbf{A5} \land \textbf{A6} \land \textbf{A7} \land \textbf{A0} \land \textbf{A1} \land \textbf{A2} \land \textbf{A3} \land \textbf{A4} \land \textbf{A5} \land \textbf{A6} \land \textbf{A7} \land \textbf{A0} \rangle $ |

|                  | Two Words per Frame                                                                                                                                                                                                                                                                        |

| Bit<br>Clock     |                                                                                                                                                                                                                                                                                            |

|                  | WC Position = 0                                                                                                                                                                                                                                                                            |

| Word             | WC Position = 1                                                                                                                                                                                                                                                                            |

|                  | WC Position = 7                                                                                                                                                                                                                                                                            |

| Data 〈 A0 〉 A1 〉 | $A2 \times A3 \times A4 \times A5 \times A6 \times A7 \times B0 \times B1 \times B2 \times B3 \times B4 \times B5 \times B6 \times B7 \times A0 $                                                                                                                                          |

Figure 5. Word-clock positioning within the data frame.

# 2.3.3. Data Framing Control

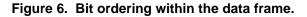

In a serial I/O interface, data is transmitted one bit at a time. However, data can be transmitted either *least-significant bit first* (LSB first), or *most-significant bit first* (MSB first), as shown in figure 6. The bit ordering used is dependent upon the requirements of the communicating systems.

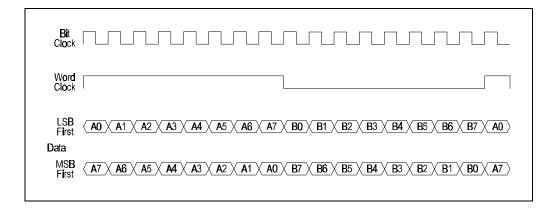

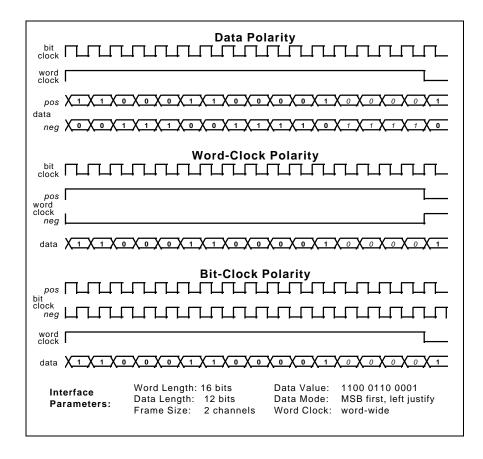

Serial interfaces may also use a *transmission word length* that is longer than the data word length (see figure 7). This is usually the case when the length of the data word being transmitted is not a multiple of eight. For example, 12-bit data may be transmitted over a serial interface that utilizes a 16-bit word length. The word length is *always* greater than or equal to the data length.

When the word length differs from the data length, two issues arise: 1) how should the data be aligned in the word, and 2) what value should the unused bits take on? Serial interfaces always justify the data along the left or right side of the word. Unused bits within the frame can be filled with logic-zero or logic-one values, or they can be filled with the value of the nearest data bit (also known as *bit-extending*). Several examples are shown in figure 7. For a given interface, the data justification mode and unused bit values used depend upon the requirements of the communicating systems. The unused bits within a data frame are usually ignored by the communicating systems.

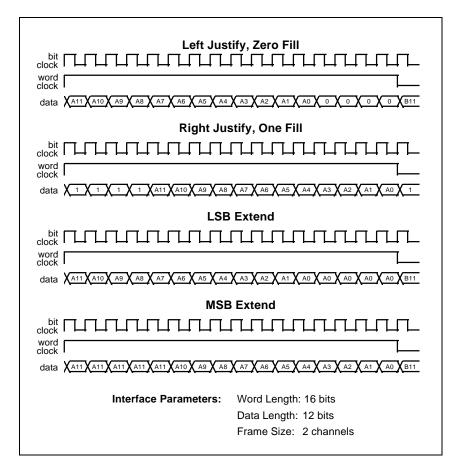

# 2.3.4. Data, Word-Clock, and Bit-Clock Polarity

The polarity of serial interface signals can vary, depending upon the needs of the communicating systems. The polarity of the serial data and word-clock signals is usually positive<sup>3</sup>. For a two-channel, word-wide word-clock signal, the positive pulse is usually associated with the first data word in the frame (that is, channel A), while the negative pulse is associated with the second word (channel B). Unlike the word-clock signal, the polarity of the bit-clock signal often differs for the transmitter and the receiver (see figure 8). In order to meet stringent data timing requirements at the receiver, the transmitter typically uses positive bit-clock polarity while the receiver uses negative bit-clock polarity.

# Figure 8. Data, word-clock and bit-clock polarity examples.

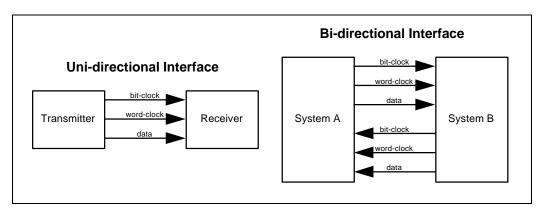

# 2.4. Serial Clocking Methods

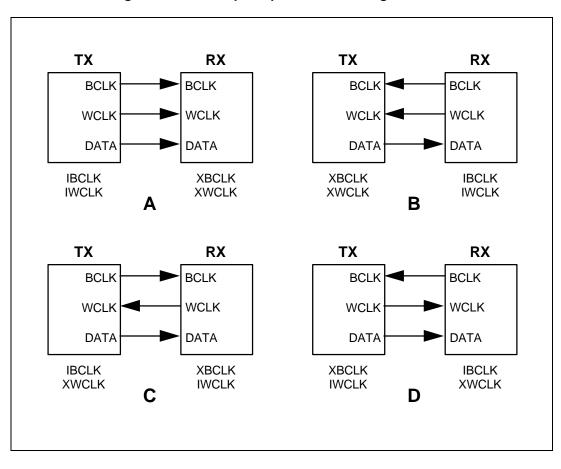

The four principal methods for interconnecting a transmitter and receiver in a communication system are shown in figures 9[A-D]. The most commonly used methods are shown in figures 9A and 9B. In 9A, the transmitter is the source of the bit-clock and word-clock signals. In this configuration, the transmitter acts as the bus *master* while the receiver acts as the bus *slave*<sup>4</sup>. In 9B, the receiver is the source of the bit-clock and word-clock signals -- here the receiver acts as the master while the transmitter acts as the slave. Figures 9C and 9D show two hybrid interconnect methods that are less commonly used. In 9C, the transmitter generates the bit-clock signal while the receiver generates the word-clock signal, and vice versa in figure 9D. Figure 9 also shows the origin of the transmitter and receiver clock sources for each of the four configurations; for example, in 9A the transmitter uses *internally* generated bit-clock (IBCLK) and word-clock (IWCLK) signals, while the receiver uses *externally* generated bit-clock (XBCLK) and word-clock (XWCLK) signals.

Figure 9. The four principal serial clocking methods.

<sup>3</sup> A positive polarity signal is one that represents logic-one bit values with a 'high' level, and logic-zero bit values with a 'low' level. A negative polarity signal is one that represents logic-one bit values with a 'low' level, and logic-zero bit values with a 'high' level.

<sup>&</sup>lt;sup>4</sup> A bus *master* is generally the device that generates the clocking signals. Non-master devices are termed *slaves* because they must synchronize their internal operation to the clock signals generated by the master.

# 3. Interfacing the SIA-2322 to the Target System

The SIA communicates with external serial devices (target systems or DUTs) through two 15-pin D-subminiature connectors or through the six BNC connectors located on the SIA front panel. The SIA user provides an interface cable with a DB-15 connector on one end, and the appropriate connections to the target system on the other end. Optionally, the user may use the six individual shielded cables connected with the BNC's.

# 3.1. Transmitter Interfacing to the Target System

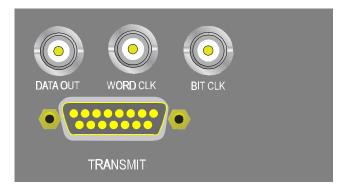

The SIA transmitter interfaces to the target system through a 15-pin male D-subminiature connector or three BNC connectors.

Five primary signals are available on the 15-pin port: serial data output, word (channel) clock I/O, bit clock I/O, N x FS clock output and reference clock input. Additionally, three tri-state control pins are provided, allowing the user to individually control the serial output, word and bit clock signals in shared-bus configurations. The pin-out for the transmitter DB-15 connector is shown in table 2 below. Note that a ground pin is associated with each primary signal. The ground pin should be used as the current return path for its corresponding signal. Three signals are available on the BNC's: serial data output, word (channel) clock I/O and bit clock I/O. The use of shielded cable is recommended for all signals.

| Signal Pin | Ground Pin | Signal Name | Signal Description           |

|------------|------------|-------------|------------------------------|

| 1          | 2          | SOD         | Serial Output Data           |

| 3          | 4          | SOWCLK      | Word Clock I/O               |

| 5          | 6          | SOBCLK      | Bit Clock I/O                |

| 7          | 8, 10      | SODE        | SOD Enable (H)               |

| 9          | 8, 10      | SOWCLKE     | SOWCLK Enable (H)            |

| 11         | 8, 10      | SOBCLKE     | SOBCLK Enable (H)            |

| 13         | 12         | TREFCLK     | Master Reference Clock Input |

|            |            |             |                              |

Serial data is transmitted on the SOD pin. The serial output word clock (SOWCLK) and bit clock (SOBCLK) signals are bi-directional; The SIA transmitter can provide the word and bit clocks necessary for data transmission (as a clock master), or it can slave to an externally-generated word or bit clock. All output drivers are capable of driving TTL or CMOS loads.

TNFSCLK

N x FS Clock Output

15

14

When configured for slave operation, the SOWCLK and SOBCLK signals can be driven by either TTL or CMOS logic. The logic family is user-selectable. Additionally, all I/O buffers are internally mounted in sockets for easy replacement.

The SIA transmitter can be used in a shared-bus configuration where the target system consists of more than one serial device. The SOD, SOWCLK and SOBCLK signals can be individually tri-stated by pulling their corresponding enable pins, SODE, SOWCLKE and SOBCLKE, low (logic zero, or ground). The SODE, SOWCLKE and SOBCLKE inputs are internally tied to +5V through 100 K-ohm resistors; these pins may be left unconnected if output tri-stating is not required. These inputs expect TTL logic levels for proper operation, however the logic loading is comparable to that of CMOS (the inputs are buffered using HCT logic family parts).

When the SIA is operated in master mode, the transmitter requires an external clock signal (applied to the TREFCLK input) which is used as the transmitter master reference clock. This signal is normally supplied by the System Two master clock output through a BNC connector to the SIA. A separate clock related to SOBCLK is provided on the TNFSCLK pin. This symmetric signal is derived directly from the reference clock. The frequency of this clock is determined by the setting of the DIV1 configuration switch (see below). This signal is not tri-stateable.

When interfacing the target system to the SIA, care must be taken in the selection of interface cabling if proper operation of the SIA and the target system is to be expected. Each of the primary signals has an associated ground pin (see table 2) which should be used as the logic reference for its corresponding signal. It is recommended that shielded cable be used for interfacing to the SIA, particularly on the SOD, SOWCLK, SOBCLK, TNFSCLK and TREFCLK lines.

All SIA inputs are internally buffered with CMOS family parts. CMOS inputs have a very high input impedance. If the interface cables are relatively long, it is recommended that all input signals be terminated at the connector to minimize reflections and ringing. A passive termination (e.g. a 75 ohm resistor connected between the input pin and its corresponding ground pin) may be used as long as the signal source is capable of providing the necessary drive current while maintaining proper logic levels. Each SIA output is capable of driving a 50 ohm transmission line, and is able to continuously source or sink at least 24 mA of current.

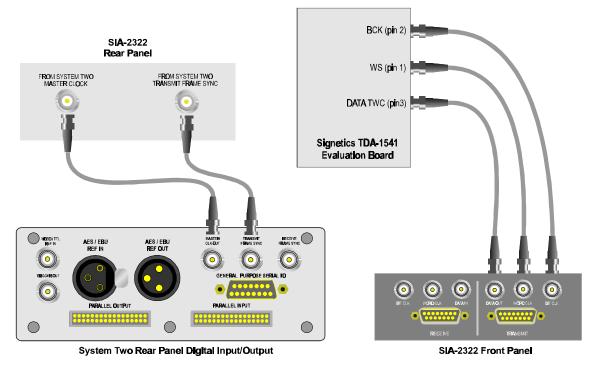

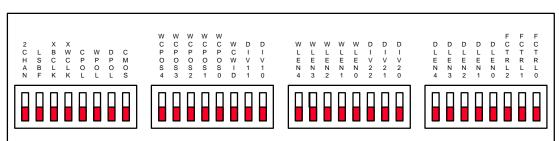

#### 3.2. Transmitter Configuration Switches

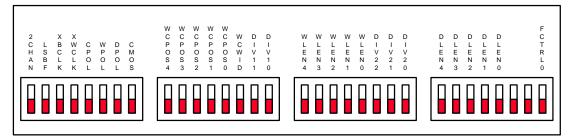

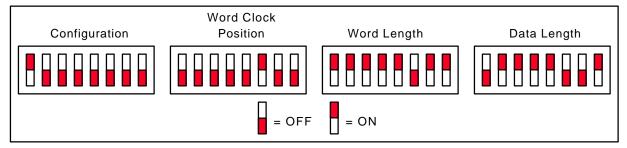

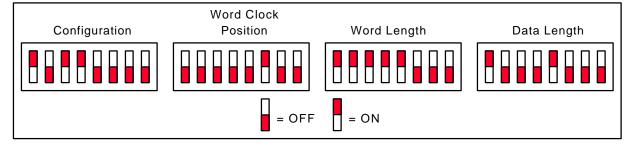

A set of DIP switches is used to configure the SIA transmitter for the various modes of operation. The switch settings for the transmitter are illustrated in figure 10 and described in table 3 below. The configuration switches can be logically grouped into four distinct groups: the serial word length select, data length select, word clock position and framing control.

#### Figure 10. Transmitter configuration switch locations.

#### 3.2.1. Serial Word Length Selection

The serial word length is the number of actual bits transmitted in each serial word. The SIA is capable of transmitting a serial word of between 8 and 32 bits in length. The word length is specified by setting the WLEN DIP switch field to the desired word length minus 1. For example, for a serial word length of 18 bits, WLEN would be set to 17, or 10001 binary.

#### 3.2.2. Serial Data Length Selection

The serial data length is the number of significant data bits to be transmitted in the serial word. System Two is capable of transmitting up to 24 bits of data per sample; However, not all target devices require a full 24 bits of data. The SIA can be programmed to truncate each sample to any number of bits from 8 to 24 (where 24 is equivalent to no truncation). The serial data length is specified by setting the DLEN DIP switch field to the desired data length minus 1. For proper SIA operation, the data length must not exceed the word length.

#### 3.2.3. Serial Word Clock Position Selection

Since the SIA transmits serial data in a synchronous manner, the word clock signal (SOWCLK) is used to delineate the start of a new serial frame. In single channel applications, "frame" is synonymous with "word." In two channel applications, a frame is composed of two words, first channel A, then channel B. The timing of SOWCLK relative to the first bit of the serial frame is set by the word clock position (WCPOS) DIP switch field. The word clock signal transitions synchronously with the transmitted data (SOD), and may be configured to transition from zero to WLEN-1 bit clock times after the start of the word. For example, if the SIA transmitter is configured for a word length of 16 bits (i.e. WLEN=01111), and the transition of SOWCLK is to occur during the last bit time of the serial frame, WCPOS would be set to 15, or 01111 binary. For proper SIA operation, the word clock position must be less than the word length.

#### 3.2.4. Serial Framing and Clocking Control

The SIA is capable of transmitting and receiving the word clock signal as either a bit-width or word-width signal, and is set by the WCWID configuration switch. If WCWID is OFF, SOWCLK will consist of a single pulse one bit-time in duration (i.e. one bit wide), transitioning at the appropriate bit time within the serial frame as defined by the setting of WCPOS. If WCWID is ON, SOWCLK will change state on each word boundary, yielding a square wave with a period equal to the serial frame time. The bit-width and word-width word clock are useful for both single- and dual-channel (time multiplexed) operation. See the section on T2CHAN below for more information.

When the data and word lengths are not the same, some control over the data within the serial word is necessary. The FCTRL0, FCTRL1 and FCTRL2 configuration switches are used to set the data-justification and sign-extension or padding of data within the word. FCTRL0 specifies whether the data within the serial word is left- or right-justified, with FCTRL0=OFF resulting in right-justified data. FCTRL1 specifies whether the data to be transmitted is sign-extended, zero padded or one padded to fit within the serial word, with FCTRL1=OFF resulting in zero or one padding. FCTRL2 specifies the bit pad value when FCTRL1=OFF; FCTRL2=OFF results in zero padding and FCTRL2=ON results in one padding.

| Switch Name | Description                                                                                                                                                                             |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2CHAN       | <b>Transmitter Channel Select</b> . OFF = single channel operation, ON = two channel operation.                                                                                         |  |  |

| LSBF        | <b>Transmitter First-Bit Select</b> . Selects LSB or MSB as first valid bit within the serial frame. OFF = MSB first, ON = LSB first.                                                   |  |  |

| XBCLK       | <b>Transmitter Bit Clock Source Select.</b> Selects source of bit clock.<br>OFF = internally generated bit clock, ON = external bit clock.                                              |  |  |

| XWCLK       | <b>Transmitter Word Clock Source Select.</b> Selects source of word clock.<br>OFF = internally generated word clock, ON = external word clock.                                          |  |  |

| CPOL        | <b>Transmitter Bit Clock Polarity Select.</b> OFF = bit clock is asserted high, ON = bit clock is inverted (asserted low).                                                              |  |  |

| WPOL        | <b>Transmitter Word Clock Polarity Select.</b> OFF = word clock is asserted high, ON = word clock is inverted (asserted low).                                                           |  |  |

| DPOL        | <b>Transmitter Data Polarity Select.</b> OFF = transmitted serial data is asserted high, ON = serial data is inverted (asserted low).                                                   |  |  |

| CMOS        | <b>Transmitter CMOS Input Select.</b> OFF = all inputs configured for TTL logic levels, ON = all inputs configured for CMOS.                                                            |  |  |

| WCPOS(4:0)  | <b>Transmitter Word Clock Position</b> . Physical position of word clock transition within the serial word. Can be set from 0 to 31.                                                    |  |  |

| WCWID       | <b>Transmitter Word Clock Width</b> . Width of transmitter word clock pulse.<br>OFF = bit-wide clock pulse, ON = word wide (symmetric) clock.                                           |  |  |

| DIV1(1:0)   | <b>Transmitter N x FS Clock Control</b> . Sets TNFSCLK frequency by selecting master reference clock divide ratio (see section 3.2.4.).                                                 |  |  |

| WLEN(4:0)   | <b>Transmitter Word Length</b> . Length of transmitted serial word, minus 1. Can be set from 7 to 31, corresponding to word lengths of 8 to 32 bits.                                    |  |  |

| DIV2(2:0)   | <b>Transmitter Bit Clock Frequency Control</b> . Sets bit clock frequency to 1/(DIV2+1) times TNFSCLK frequency (see section 3.2.4.).                                                   |  |  |

| DLEN(4:0)   | <b>Transmitter Data Length</b> . Number of significant bits of System Two data word to be transmitted, minus 1. Can be set from 7 to 23, corresponding to data lengths of 8 to 24 bits. |  |  |

| FCTRL0      | <b>Transmitter Framing Control 0</b> . OFF = right-justified data within the serial frame, ON = left-justified.                                                                         |  |  |

| FCTRL1      | <b>Transmitter Framing Control 1</b> . OFF = zero/one pad out-of-bounds data,<br>ON = sign extend out-of-bounds data.                                                                   |  |  |

| FCTRL2      | <b>Transmitter Framing Control 2</b> . If FCTRL1 = OFF, sets pad value for out-<br>of-bounds data. OFF = zero, ON = one.                                                                |  |  |

The SIA is capable of transmitting a single channel of data from System Two, or two channels of data in a time-multiplexed fashion. The mode of operation is set by the 2CHAN configuration switch. When 2CHAN=OFF, a single channel of data from System Two (the B channel) is transmitted. When 2CHAN=ON, two channels of data are transmitted (channels A and B). In two-channel mode with WCWID=ON (word-width word clock), the direction of transition of SOWCLK determines which channel is being transmitted at any given time. When

WPOL=OFF (see below), a low-to-high transition within the data frame implies that channel A is being transmitted. In a similar manner, a high-to-low transition implies that channel B is being transmitted. In two-channel mode with WCWID=OFF (bit-width word clock) and WPOL=OFF, a low-to-high transition of SOWCLK signals the start of a new serial frame, with channel A transmitted first, followed by channel B.

The data sample may be transmitted either most significant bit (MSB) first, or least significant bit (LSB) first. The order is controlled by the LSBF configuration switch. When LSBF=OFF, the data is transmitted MSB first. When LSBF=ON, the data is transmitted LSB first.

The SIA transmitter is capable of generating a bit clock and word clock derived directly from the master reference clock (TREFCLK) input. Optionally, one or both of these clocks can be generated by the target system and supplied to the SIA, which will subsequently behave in a slave-transmitter fashion. The source of the word clock is defined by the state of the XWCLK configuration switch. If XWCLK=OFF, the transmitter will drive SOWCLK with a locally generated word clock. If XWCLK=ON, the transmitter will slave to the word clock signal received on SOWCLK from the target system. In a similar manner, if XBCLK=OFF the transmitter will drive SOBCLK with a locally generated bit clock. If XBCLK=OFF the transmitter will slave to the bit clock received on SOBCLK from the target system. The four possible operating modes are shown in table 4 below. Note that clocks supplied by the target system must be appropriate for a given transmitter configuration (i.e. the number of bit clocks per word clock interval must match the setting of WLEN, etc.).

| XBCLK | XWCLK | Transmitter Clock Source                                                                       |

|-------|-------|------------------------------------------------------------------------------------------------|

| OFF   | OFF   | Bit clock and word clock derived directly from master reference clock (TREFCLK).               |

| OFF   | ON    | Not useful.                                                                                    |

| ON    | OFF   | Bit clock from target system used to generate word clock (TREFCLK generates TNFSCLK only).     |

| ON    | ON    | Bit clock and word clock derived directly from target system (TREFCLK generates TNFSCLK only). |

The polarity of the transmitted data, word and bit clocks are controlled by the DPOL, WPOL and CPOL configuration switches. When DPOL=OFF, serial data is transmitted using positive logic levels. When DPOL=ON, the transmitted data is inverted.

The WPOL configuration switch allows the user to change the logic sense of SOWCLK when WCWID=OFF (i.e. word clock is bit-wide), and to change the channel sense when WCWID=ON. As described above, when WPOL=OFF and WCWID=ON, a low-to-high transition within the data frame implies that channel A is being transmitted. In a similar manner, a high-to-low transition implies that channel B is being transmitted. When WPOL=ON, the channel sense is reversed.

CPOL is used to define which edge of SOBCLK the serial data (SOD) and serial output word (SOWCLK) transition on. When CPOL=OFF, both SOD and SOWCLK transition on the rising edge of SOBCLK. When CPOL=ON, both SOD and SOWCLK transition on the falling edge of

SOBCLK. When SOWCLK is configured as an input, CPOL defines which edge of SOBCLK samples SOWCLK. With CPOL=OFF, SOWCLK is sampled on the rising edge. With CPOL=ON, SOWCLK is sampled on the falling edge.

When configured as inputs, SOBCLK and SOWCLK can be configured to accept TTL or CMOS logic levels. The logic family is selected by the CMOS configuration switch. When CMOS=OFF, both inputs expect TTL logic levels. When CMOS=ON, both inputs expect CMOS logic levels. In either configuration, input loading is very low (inputs are buffered using HC/HCT logic family parts).

The DIV1 configuration switch field is used to select the frequency of the N x FS clock (TNFSCLK) signal. The TNFSCLK signal is generated by a power-of-two divider driven by the master reference clock (TREFCLK). DIV1 selects one of four possible division ratios: 1, 2, 4, or 8. The power-of-two divider may optionally be configured to divide by 4, 8, 16, or 32; this mode is described in section 3.6. below. The DIV1 switch is typically used in conjunction with the DIV2 switch to generate a clock that is a multiple of the system sample rate.

The DIV2 configuration switch field is used to set the bit clock (SOBCLK) frequency, and is derived from the N x FS clock signal. The transmitter bit clock is generated by a divider driven by TNFSCLK, where DIV2 is used to select the divide ratio. DIV2 selects one of eight possible division ratios: 1, 2, 3, 4, 5, 6, 7, or 8. DIV2 is typically used in conjunction with the DIV1 switch. For example, if TREFCLK is driven by a 12.288 MHz clock and the system is configured for two channels of 32-bit words at a sample rate of 48 kHz, the N x FS clock and bit clocks may be configured as follows: for a 256 x FS clock on TNFSCLK, DIV1 would be set to divide-by-one (DIV1 = 00 binary) and DIV2 would be set to divide-by-four (DIV2 = 011 binary); for a 128 x FS clock, DIV1 would be set to divide-by-two (DIV1 = 01 binary) and DIV2 would be set to divide-by-two (DIV2 = 001 binary). Note that in each of the above examples, the bit clock frequency remains constant (3.072 MHz) since the product of DIV1 and DIV2 is constant. Other N x FS clocks can be generated by the appropriate choice of reference clock frequency and DIV1 and DIV2 settings.

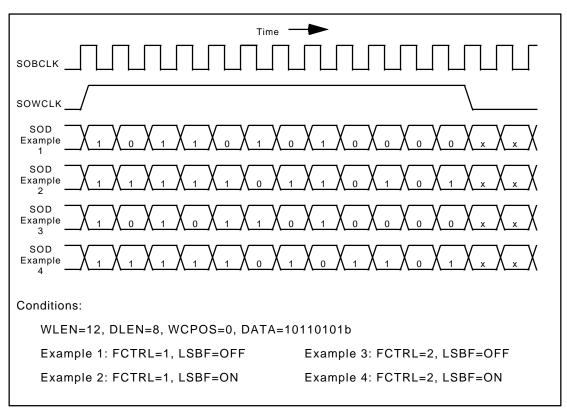

# 3.2.5. Serial Framing Examples

Figure 11 below shows some examples of serial data framing from four different transmitter configurations. The figure, illustrates four typical serial waveforms generated by the SIA on the SOD pin. All four configurations assume that WLEN=12, DLEN=8, WCPOS=0, and the data being transmitted is 10110101 binary. In examples 1 and 2, LSBF=OFF yields a waveform where the MSB is transmitted first. In examples 3 and 4, LSBF=ON yields a waveform where the LSB is transmitted first. In examples 1 and 3, the data in the frame is left-justified and zero-padded, while in examples 2 and 4, the data is right-justified and bit-extended (MSB-extended in example 2, LSB-extended in example 4).

Figure 11. Serial output framing examples.

# 3.3. Receiver Interfacing to the Target System

The SIA receiver interfaces to the target system through a 15-pin female D-subminiature connector or three BNC connectors.

Five primary signals are available on the 15-pin port: serial data input, word (channel) clock I/O, bit clock I/O, N x FS clock output and master reference clock input. Additionally, two tristate control pins are provided, allowing the user to individually control the serial word and bit clock signals in shared-bus configurations. The pin-out for the receiver DB-15 connector is shown in table 5 below. Note that a ground pin is associated with each primary signal. The ground pin should be used as the current return path for its corresponding signal. Three signals are available on the BNC's; serial data input, word (channel) clock I/O and bit clock I/O. The use of shielded cable is recommended for all signals. Serial data is received on the SID pin. The serial input word clock (SIWCLK) and bit clock (SIBCLK) signals are bi-directional; The SIA receiver can provide the word and bit clocks necessary for data transmission when a master reference clock is supplied, or it can slave to an externally-generated word or bit clock. All output drivers are capable of driving TTL or CMOS loads. When configured for slave operation, the SIWCLK and SBCLK signals can be driven by either TTL or CMOS logic. The logic family is user-selectable. Additionally, all I/O buffers are internally mounted in sockets for easy replacement.

| Signal Pin | Ground Pin | Signal Name | Signal Description           |

|------------|------------|-------------|------------------------------|

| 1          | 2          | SID         | Serial Input Data            |

| 3          | 4          | SIWCLK      | Word Clock I/O               |

| 5          | 6          | SIBCLK      | Bit Clock I/O                |

| 7          |            |             | No Connection                |

| 9          | 8, 10      | SIWCLKE     | SIWCLK Enable (H)            |

| 11         | 8, 10      | SIBCLKE     | SIBCLK Enable (H)            |

| 13         | 12         | RREFCLK     | Master Reference Clock Input |

| 15         | 14         | RNFSCLK     | N x FS Clock Output          |

| Table 5. | SIA receiver seria | I connector pin assignment. |

|----------|--------------------|-----------------------------|

|----------|--------------------|-----------------------------|

The SIA receiver can be used in a shared-bus configuration where the target system consists of more than one serial device. The SIWCLK and SIBCLK signals can be individually tri-stated by pulling their corresponding enable pins, SIWCLKE and SIBCLKE, low (logic zero, or ground). The SIWCLKE and SBCLKE inputs are internally tied to +5V through 100 K-ohm resistors; these pins may be left unconnected if output tri-stating is not required. These inputs expect TTL logic levels for proper operation, however the logic loading is comparable to that of CMOS (the inputs are buffered using HCT logic family parts).

When the SIA is used in master mode, the receiver requires an external clock (applied to the RREFCLK input) which is used as the receiver master reference clock. A separate clock related to SIBCLK is provided on the RNFSCLK pin. This symmetric signal is derived directly from the reference clock. The frequency of this clock is determined by the setting of the DIV1 configuration switch (see below). This signal is not tri-stateable.

When interfacing the target system to the SIA, care must be taken in the selection of interface cabling if proper operation of the SIA and the target system is to be expected. Each of the primary signals has an associated ground pin (see table 5) which should be used as the logic reference for its corresponding signal. It is recommended that shielded cable be used for interfacing to the SIA, particularly on the SID, SIWCLK, SIBCLK, RNFSCLK and RREFCLK lines.

All SIA inputs are internally buffered with CMOS family parts. CMOS inputs have a very high input impedance. If the interface cables are relatively long, it is recommended that all input signals be terminated at the connector to minimize reflections and ringing. A passive termination (e.g. a 75 ohm resistor connected between the input pin and its corresponding ground pin) may be used as long as the signal source is capable of providing the necessary drive current while maintaining proper logic levels. Each SIA output is capable of driving a 50 ohm transmission line, and is able to continuously source or sink at least 24 mA of current.

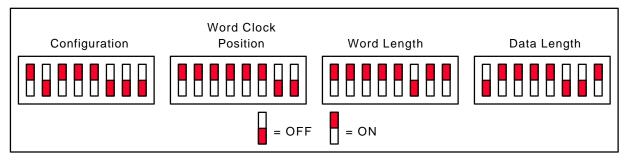

# 3.4. Receiver Configuration Switches

A set of DIP switches is used to configure the SIA receiver for the various modes of operation. The switch settings for the receiver are illustrated in Figure 12 and described in table 6 below. The configuration switches can be logically grouped into four distinct groups: the serial word length select, data length select, word clock position and framing control.

Figure 12. Receiver configuration switch locations.

# 3.4.1. Serial Word Length Selection

The serial word length is the number of actual bits received in each serial word. The SIA is capable of receiving a serial word of between 8 and 32 bits in length. The word length is specified by setting the WLEN DIP switch field to the desired word length minus 1. For example, for a serial word length of 18 bits, WLEN would be set to 17, or 10001 binary.

# 3.4.2. Serial Data Length Selection

The serial data length is the number of significant data bits to be received in the serial word. System Two is capable of receiving up to 24 bits of data per sample; However, not all target devices are capable of supplying a full 24 bits of data. The SIA can be programmed to truncate each received data sample to any number of bits from 8 to 24. The serial data length is specified by setting the DLEN DIP switch field to the desired data length minus 1. For proper SIA operation, the data length must not exceed the word length.

# 3.4.3. Serial Word Clock Position Selection

Since the SIA receives serial data in a synchronous manner, the word clock signal (SIWCLK) is used to delineate the start of a new serial frame. In single channel applications, "frame" is synonymous with "word." In two channel applications, a frame is composed of two words, first channel A, then channel B. The timing of SIWCLK relative to the first bit of the serial frame can be configured by setting the word clock position (WCPOS) DIP switch field. The word clock signal transitions synchronously with the received data (SID), and the timing of word clock relative to the start of a received data frame may be set from zero to WLEN-1 bit clock times after the start of the word. For example, if the SIA receiver is configured for a word length of 16 bits (i.e. WLEN=01111), and the transition of SIWCLK is to occur during the last bit time of the serial frame, WCPOS would be set to 15, or 01111 binary. For proper SIA operation, the word clock position must be less than the word length.

| Switch Name | Description                                                                                                                                                                                              |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2CHAN       | <b>Receiver Channel Select</b> . OFF = single channel operation, ON = two channel operation.                                                                                                             |  |  |

| LSBF        | <b>Receiver First-Bit Select</b> . Selects LSB or MSB as first valid bit within the serial frame. OFF = MSB first, ON = LSB first.                                                                       |  |  |

| XBCLK       | <b>Receiver Bit Clock Source Select.</b> Selects source of bit clock.<br>OFF = internally generated bit clock, ON = external bit clock.                                                                  |  |  |

| XWCLK       | <b>Receiver Word Clock Source Select.</b> Selects source of word clock.<br>OFF = internally generated word clock, ON = external word clock.                                                              |  |  |

| CPOL        | <b>Receiver Bit Clock Polarity Select.</b> OFF = bit clock is asserted high,<br>ON = bit clock is inverted (asserted low).                                                                               |  |  |

| WPOL        | <b>Receiver Word Clock Polarity Select.</b> OFF = word clock is asserted high, ON = word clock is inverted (asserted low).                                                                               |  |  |

| DPOL        | <b>Receiver Data Polarity Select.</b> OFF = received serial data is asserted high, ON = serial data is inverted (asserted low).                                                                          |  |  |

| CMOS        | <b>Receiver CMOS Input Select.</b> OFF = all inputs configured for TTL logic levels, ON = all inputs configured for CMOS.                                                                                |  |  |

| WCPOS(4:0)  | <b>Receiver Word Clock Position</b> . Physical position of word clock transition within the serial word. Can be set from 0 to 31.                                                                        |  |  |

| WCWID       | <b>Receiver Word Clock Width</b> . Width of receiver word clock pulse.<br>OFF = bit-wide clock pulse, ON = word wide (symmetric) clock.                                                                  |  |  |

| DIV1(1:0)   | <b>Receiver N x FS Clock Control</b> . Sets RNFSCLK frequency by selecting master reference clock divide ratio (see section 3.4.4.).                                                                     |  |  |

| WLEN(4:0)   | <b>Receiver Word Length</b> . Length of received serial word, minus 1. Can be set from 7 to 31, corresponding to word lengths of 8 to 32 bits.                                                           |  |  |

| DIV2(2:0)   | <b>Receiver Bit Clock Frequency Control</b> . Sets bit clock frequency to 1/(DIV2+1) times RNFSCLK frequency (see section 3.4.4.).                                                                       |  |  |

| DLEN(4:0)   | <b>Receiver Data Length</b> . Number of significant bits from received serial word to be transmitted to the System Two, minus 1. Can be set from 7 to 23, corresponding to data lengths of 8 to 24 bits. |  |  |

| FCTRL0      | <b>Receiver Framing Control 0</b> . OFF = right-justified data within the serial frame, ON = left-justified.                                                                                             |  |  |

# 3.4.4. Serial Framing and Clocking Control

The SIA is capable of transmitting and receiving the word clock signal as either a bit-width or word-width signal, and is set by the WCWID configuration switch. If WCWID=OFF, SIWCLK will consist of a single pulse one bit-time in duration (i.e. one bit wide), transitioning at the appropriate bit time within the serial frame as defined by the setting of WCPOS. If WCWID=ON, SIWCLK will change state on each word boundary, effectively yielding a square wave with a period equal to the serial frame time. The bit-width and word-width word clock are useful for both single- and dual-channel (time multiplexed) operation. See the section on 2CHAN below for more information.

When the data and word lengths are not the same, it is necessary to specifying whether the data is left- or right-justified within the data word. FCTRL0 is used to specify this configuration.

When FCTRL0=OFF, the received data is expected to be right-justified within the data word. When FCTRL0=ON, the received data is expected to be left-justified within the word.

The SIA is capable of receiving a single channel of data from the target system, or two channels of data in a time-multiplexed fashion. The mode of operation is set by the 2CHAN configuration switch. When 2CHAN=OFF, a single channel of data from the target system is received and transferred to System One (the B channel). When 2CHAN=ON, two channels of data are received (channels A and B). In two-channel mode with WCWID=ON (word-width word clock), the direction of transition of SIWCLK determines which channel is being received at any given time. When WPOL=OFF (see below), a low-to-high transition within the data frame implies that channel A is being received. In a similar manner, a high-to-low transition implies that channel B is being received. In two-channel mode with WCWID=OFF (bit-width word clock) and WPOL=OFF, a low-to-high transition of SIWCLK signals the start of a new serial frame, with channel A received first, followed by channel B.

The data sample within the frame may be sent by the target system either most significant bit (MSB) first, or least significant bit (LSB) first. The receiver can be configured for data in either format by setting LSBF to match the desired configuration. When LSBF=OFF, the received data is expected to be sent MSB first. When LSBF=ON, the received data is expected to be sent LSB first.

The SIA receiver is capable of generating a bit clock and word clock derived directly from the master reference clock (RREFCLK) input. Optionally, one or both of these clocks can be generated by the target system and supplied to the SIA, which will subsequently behave in a slave-receiver fashion. The source of the word clock is defined by the state of the XWCLK configuration switch. If XWCLK=OFF, the receiver will drive SIWCLK with a locally generated word clock. If XWCLK=ON, the receiver will slave to the word clock signal received on SIWCLK from the target system. In a similar manner, if XBCLK=OFF the receiver will drive SIBCLK with a locally generated bit clock. If XBCLK=ON, the receiver will slave to the bit clock received on SIBCLK from the target system. The four possible operating modes are shown in table 7 below. Note that clocks supplied by the target system must be appropriate for a given receiver configuration (i.e. the number of bit clocks per word clock interval must match the setting of WLEN, etc.).

The polarity of the received data, word and bit clocks are controlled by the DPOL, WPOL and CPOL configuration switches. When DPOL=OFF, serial data received is transferred to System Two without modification (subject to the setting of DLEN, etc.). When DPOL=ON, the received data is inverted prior to transmission to System Two.

The WPOL configuration switch allows the user to change the logic sense of SIWCLK when WCWID=OFF (i.e. word clock is bit-wide), and to change the channel sense when WCWID=ON. As described above, when WPOL=OFF and WCWID=ON, a low-to-high transition within the data frame implies that channel A is being received. In a similar manner, a high-to-low transition implies that channel B is being received. When WPOL=ON, the channel sense is reverse.

| XBCLK | XWCLK | Receiver Clock Source                                                                          |  |

|-------|-------|------------------------------------------------------------------------------------------------|--|

| OFF   | OFF   | Bit clock and word clock derived directly from master reference clock (RREFCLK).               |  |

| OFF   | ON    | Not useful.                                                                                    |  |

| ON    | OFF   | Bit clock from target system used to generate word clock (RREFCLK generates RNFSCLK only).     |  |

| ON    | ON    | Bit clock and word clock derived directly from target system (RREFCLK generates RNFSCLK only). |  |

| Table 7. | Receiver  | clock | source | selection.  |

|----------|-----------|-------|--------|-------------|

|          | 110001101 | 01001 | 300100 | 3010011011. |

CPOL is used to define which edge of SIBCLK the received data (SID) and/or word clock (SIWCLK) are sampled on. When CPOL=OFF, both SID and SIWCLK are sampled on the rising edge of SIBCLK. When CPOL=ON, SID and SIWCLK are sampled on the falling edge of SIBCLK. When SIWCLK is configured as an output, CPOL defines which edge of SIBCLK that SIWCLK transitions on. When CPOL=OFF, SIWCLK transitions on the rising edge of SIBCLK. When CPOL=ON, SIWCLK transitions on the falling edge.

When configured as inputs, SIBCLK and SIWCLK can be configured to accept TTL or CMOS logic levels. The logic family is selected by the CMOS configuration switch. When CMOS=OFF, both inputs expect TTL logic levels. When CMOS=ON, both inputs expect CMOS logic levels. In either configuration, input loading is very low (inputs are buffered using HC/HCT logic family parts).

The DIV1 configuration switch field is used to select the frequency of the N x FS clock (RNFSCLK) signal. The RNFSCLK signal is generated by a power-of-two divider driven by the master reference clock (RREFCLK). DIV1 selects one of four possible division ratios: 1, 2, 4, or 8. The power-of-two divider may optionally be configured to divide by 4, 8, 16, or 32; this mode is described in section 3.6. below. The DIV1 switch is typically used in conjunction with the DIV2 switch to generate a clock that is some multiple of the system sample rate.

The DIV2 configuration switch field is used to set the bit clock (SIBCLK) frequency, and is derived from the N x FS clock signal. The transmitter bit clock is generated by a divider driven by RNFSCLK, where DIV2 is used to select the divide ratio. DIV2 selects one of eight possible division ratios: 1, 2, 3, 4, 5, 6, 7, or 8. DIV2 is typically used in conjunction with the DIV1 switch. For example, if RREFCLK is driven by a 12.288 MHz clock and the system is configured for two channels of 32-bit words at a sample rate of 48 kHz, the N x FS clock and bit clocks may be configured as follows: for a 256 x FS clock on RNFSCLK, DIV1 would be set to divide-by-one (DIV1 = 00 binary) and DIV2 would be set to divide-by-four (DIV2 = 011 binary); for a 128 x FS clock, DIV1 would be set to divide-by-two (DIV1 = 01 binary) and DIV2 would be set to divide-by-two (DIV2 = 001 binary). Note that in each of the above examples, the bit clock frequency remains constant (3.072 MHz) since the product of DIV1 and DIV2 is constant. Other N x FS clocks can be generated by the appropriate choice of reference clock frequency and DIV1 and DIV2 settings.

#### 3.5. System Performance Issues

One of the most critical parameters affecting high-performance A/D and D/A converter systems is clock jitter. Many high-precision converter systems require bit, word, or reference

clocks with residual jitter of less than 200 pS RMS. While the SIA is capable of generating clocks with residual jitter in the 100 to 200 pS range, optimum performance is achieved when reference clocks derived from a crystal oscillator are used to drive both the converter system and the SIA in slave mode (many A/D and D/A evaluation boards provide crystal-derived low-jitter bit and word clocks that are ideal for driving the SIA). When using a crystal oscillator for the system reference, great care must be taken in the interface between the SIA and the converter system. Attention must be paid to the quality and length of the interface cables, as well as signal terminations at the SIA and the system I/O connectors.

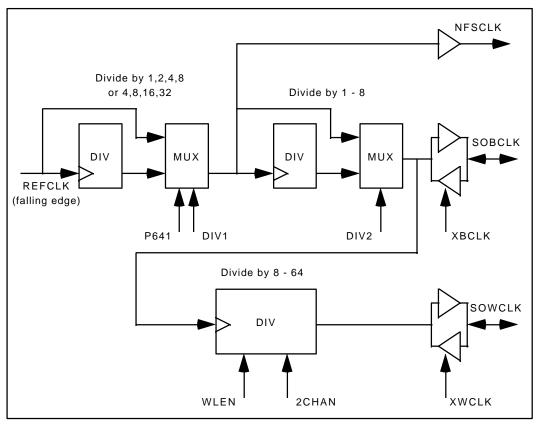

When using the SIA to generate bit and word clocks, the SIA uses the falling edge of the reference clock to drive the system dividers. In such instances, the reference clock used to drive the SIA should be optimized to have minimum jitter on its falling edge. Figure 13 below shows the internal clock divider chain for the transmitter section of the SIA that is used to generate bit and word clocks from an external reference. The internal clock divider chain for the receiver section of the SIA is identical to that shown in the figure.

# 3.6. Transmitter and Receiver N x FS Clock Control

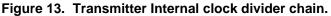

The N x FS clocks of the transmitter and receiver (TNFSCLK and RNFSCLK, respectively) are generated by programmable dividers on the SIA circuit board. As shipped from the factory, the transmitter and receiver dividers can be independently programmed to divide by 1, 2, 4, or 8 by way of the front panel configuration switches DIV1. Each divider can alternatively be configured to divide by 4, 8, 16, or 32 for those applications that require higher divide ratios. This mode is configured via two jumpers located on the SIA circuit board. The jumpers are

accessible by removing the top cover of the SIA. Referring to figure 14, jumper P641 is used to select the divide range for the transmitter, and jumper P591 is used to select the divide range for the receiver. The appropriate configuration of the jumpers for each mode is shown in the figure.

Figure 14. Location of P641 and P591 jumpers on SIA circuit board.

# 4. Serial Interface Timing

# 4.1. Transmitter I/O Timing

Table 8 below defines the various AC timing characteristics of the SIA transmitter. All timing information is measured at the DB-15 connector and assumes an output loading capacitance of 50 pF and an operating temperature of 25 degrees C.

| Parameter                               | XBCLK | XWCLK | Min | Typical | Max | Units |

|-----------------------------------------|-------|-------|-----|---------|-----|-------|

| TREFCLK period                          | -     | -     | 65  | -       | -   | nS    |

| SOBCLK to SOD delay                     | OFF   | -     | 0   | 2       | 20  | nS    |

| SOBCLK to SOD delay                     | ON    | -     | -   | 42      | 58  | nS    |

| SOBCLK to SOWCLK delay                  | OFF   | OFF   | 0   | 12      | 41  | nS    |

| SOBCLK to SOWCLK delay                  | ON    | OFF   | -   | 53      | 69  | nS    |

| SOWCLK to SOBCLK setup                  | OFF   | ON    | 53  | -       | -   | nS    |

| SOWCLK to SOBCLK hold                   | OFF   | ON    | 0   | -       | -   | nS    |

| SOWCLK to SOBCLK setup                  | ON    | ON    | 10  | -       | -   | nS    |

| SOWCLK to SOBCLK hold                   | ON    | ON    | 0   | -       | -   | nS    |

| SOD, SOWCLK, SOBCLK output enable time  | -     | -     | -   | 16      | 24  | nS    |

| SOD, SOWCLK, SOBCLK output disable time | -     | -     | -   | 17      | 24  | nS    |

Table 8.

Transmitter AC Timing Characteristics

# 4.2. Receiver I/O Timing

Table 9 below defines the various AC timing characteristics of the SIA receiver. All timing information is measured at the DB-15 connector and assumes an output loading capacitance of 50 pF and an operating temperature of 25 degrees C.

| Parameter                            | XBCLK | XWCLK | Min | Typical | Max | Units |

|--------------------------------------|-------|-------|-----|---------|-----|-------|

| RREFCLK period                       | -     | -     | 65  | -       | -   | nS    |

| SIBCLK to SIWCLK delay               | OFF   | OFF   | 0   | 12      | 42  | nS    |

| SIBCLK to SIWCLK delay               | ON    | OFF   | -   | 53      | 70  | nS    |

| SIWCLK to SID setup                  | OFF   | -     | 53  | -       | -   | nS    |

| SIWCLK to SID hold                   | OFF   | -     | 0   | -       | -   | nS    |

| SIWCLK to SID setup                  | ON    | -     | 10  | -       | -   | nS    |

| SIWCLK to SID hold                   | ON    | -     | 0   | -       | -   | nS    |

| SIWCLK to SIBCLK setup               | OFF   | ON    | 53  | -       | -   | nS    |

| SIWCLK to SIBCLK hold                | OFF   | ON    | 0   | -       | -   | nS    |

| SIWCLK to SIBCLK setup               | ON    | ON    | 10  | -       | -   | nS    |

| SIWCLK to SIBCLK hold                | ON    | ON    | 0   | -       | -   | nS    |

| SIWCLK, SIBCLK output<br>enable time | -     | -     | -   | 16      | 24  | nS    |

| SIWCLK, SIBCLK output disable time   | -     | -     | -   | 17      | 24  | nS    |

Table 9. Receiver AC Timing Characteristics

# 5. SIA-DUT Interfacing Examples

This section presents a number of examples of interconnections to typical devices

# 5.1. Configuring the SIA for Local Loopback

The SIA can be easily configured for *loopback* operation by connecting three BNC to BNC cables between the TRANSMIT and RECEIVE data signals. The two parallel interface cables and both BNC cables must be connected between the rear panels of the SIA and the System Two. The term *loopback* refers to the physical connection of the SIA transmitter's serial I/O lines to the receiver's lines. Data sent by the SIA transmitter is simultaneously received by the receiver. Loopback operation is helpful for verifying proper SIA hardware operation and experimenting with various serial configurations.

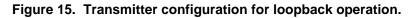

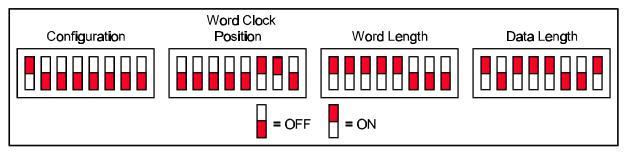

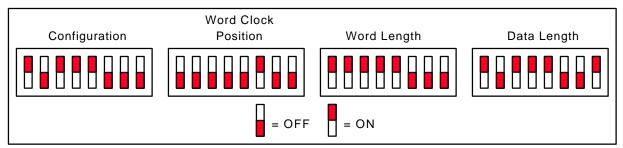

In this loopback configuration, the transmitter is configured as the system master and the receiver as the slave. The data rate is 48 kHz with two 24-bit words transmitted per 64-bit frame. The correct configuration switch settings for the transmitter and receiver are shown in figures 15 and 16 below. The transmitter receives its clock signal from the master clock output of the System Two (for this example, it is assumed that the System Two sample rate is set to 48 kHz, making the System Two master clock output frequency 12.288 MHz).

#### 5.2. Connecting the SIA Receiver to the Crystal CDB5336 Evaluation Board

The Crystal CDB5336 Evaluation Board is used to evaluate the Crystal CS5336 dualchannel analog-to-digital converter. The CS5336 is a particularly interesting converter as it can be configured for either master or slave operation, each having different interface requirements. The SIA receiver can interface properly to the CS5336 in either mode.

# 5.2.1. The Crystal CDB5336 in Slave Mode

When the CS5336 is configured as a slave device, the SIA receiver operates as the master, thereby generating the bit, word, and high-frequency clocks for the CS5336. In order to correctly drive the CS5336 in this mode, you must make the following changes to the CDB5336 evaluation board:

- **D** Remove R6, the clock termination resistor

- □ Set P4 to '5336/38'

- □ Set P5 to 'B'

- □ Set P6 to 'zero'

- □ Set P7 to 'external'

- □ Set P8, P9 to 'in'

- Connect SMODE (pin **13** on the CS5336) to ground (LOW).

- Connect FSYNC (pin 17 on the CS5336) to VCC (HIGH).

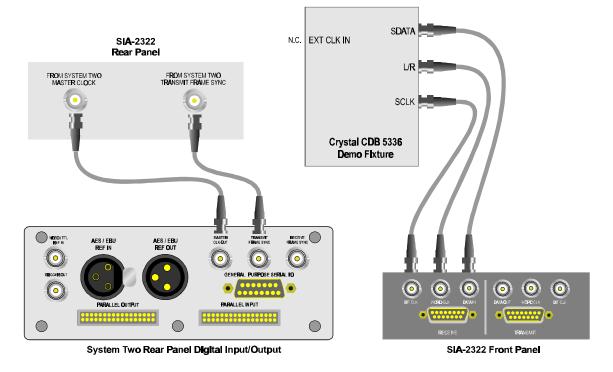

The connections necessary between the SIA-2322 and the CDB5336 board are described in table 10 and shown in figure 17. The proper configuration switch settings for the SIA receiver are shown in figure 18.

| SIA-2322 / SystemCDB5336 BoardTwo ConnectionsConnection |          | Signal Description                         |

|---------------------------------------------------------|----------|--------------------------------------------|

| Data In                                                 | SDATA    | Serial Data from CDB5336 to SIA            |

| Word Clock                                              | L/R      | Word Clock from SIA to CDB5336             |

| Bit Clock                                               | SCLK     | Bit Clock from SIA to CDB5336              |

| System Two Mstr Clk                                     | EXTCLKIN | Reference Clock from System Two to CDB5336 |

Table 10. SIA-2322 / CDB5336 interconnection (CDB5336 as slave).

Figure 18. SIA receiver configuration for CDB5336 as slave.

#### 5.2.2. The Crystal CDB5336 in Master Mode

When the CS5336 is configured as a master device (with the SIA operating as the slave), the CS5336 generates the bit and word clocks for the SIA. To correctly configure the CDB5336 evaluation board for master mode operation, you must make the following changes to the board:

- Remove R6, the clock termination resistor

- □ Set P4 to '5336/38'

- □ Set P5 to 'B'

- □ Set P6 to 'zero'

- □ Set P7 to 'internal'

- □ Set P8, P9 to 'in'

The connections necessary between the SIA-2322 and the CDB5336 board are described in table 11 and shown in figure 19. The proper configuration switch settings for the SIA receiver are shown in figure 20. Note that the CS5336 in Master mode transmits data in a manner compatible with the Signetics  $I^2S$  Bus Standard.

| SIA-2322<br>Connectio<br>n | CDB5336 Board<br>Connection | Signal<br>Description           |

|----------------------------|-----------------------------|---------------------------------|

| Data In                    | SDATA                       | Serial Data from CDB5336 to SIA |

| Word Clock                 | L/R                         | Word Clock from CDB5336 to SIA  |

| Bit Clock                  | SCLK                        | Bit Clock from CDB5336 to SIA   |

#### Table 11. SIA-2322 / CDB5336 interconnection (CDB5336 as master).

# Figure 19. Receiver / CDB5336 physical interconnection (CDB5336 as master).

Figure 20. SIA receiver configuration for CDB5336 in master mode.

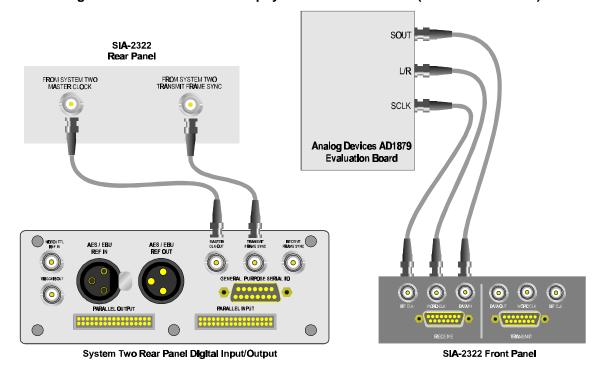

#### 5.3. Connecting the SIA Receiver to the Analog Devices AD1879 Evaluation Board

The Analog Devices AD1879 is a dual-channel, 18-bit analog-to-digital converter capable of both master and slave mode operation. The SIA can interface properly to the AD1879 in either mode. This example shows how to connect the SIA to the AD1879 evaluation board when the AD1879 is configured for master operation.

In master mode, the AD1879 generates the bit and word clocks for the SIA. To correctly configure the AD1879 board for master mode operation, make the following changes to the board:

- **D** Remove jumper JP1

- □ Install jumpers JP2-7

- □ Set switch SW1 for internal reference clock

The connections necessary between the SIA-2322 and the AD1879 evaluation board are described in table 12 and shown in figure 21. The proper configuration switch settings for the SIA receiver are shown in figure 22.

| SIA-2322<br>Connection | AD1879 Board<br>Connection | Signal<br>Description          |

|------------------------|----------------------------|--------------------------------|

| Data In                | SOUT                       | Serial Data from AD1879 to SIA |

| Word Clock             | L/R                        | Word Clock from AD1879 to SIA  |

| Bit Clock              | SCLK                       | Bit Clock from AD1879 to SIA   |

|                        |                            |                                |

#### Table 12. SIA-2322 / AD1879 evaluation board interconnection (AD1879 as master).

Figure 21. Receiver / AD1879 physical interconnection (AD1879 as master).

| Figure 22. | SIA receiver configuration for AD1879 in master mode. |

|------------|-------------------------------------------------------|

|------------|-------------------------------------------------------|

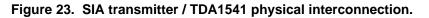

# 5.4. Connecting the SIA Transmitter to the Signetics TDA1541

The Signetics TDA1541 is a dual-channel, 16-bit digital-to-analog converter that can be configured for the I<sup>2</sup>S Bus Standard. The connections necessary between the SIA-2322 and the TDA1541 are described in table 13 and shown in figure 23. The proper configuration switch settings for the SIA transmitter are shown in figure 24.

| SIA-DUT Interface<br>Board Connection | TDA1541<br>Connection | Signal<br>Description           |

|---------------------------------------|-----------------------|---------------------------------|

| Data Out                              | DATA TWC (3)          | Serial Data from SIA to TDA1541 |

| Word Clock                            | WS (1)                | Word Clock from SIA to TDA1541  |

| Bit Clock                             | BCK (2)               | Bit Clock from SIA to TDA1541   |

| Table 13. | SIA-2322 / | TDA1541 | interconnection. |

|-----------|------------|---------|------------------|

| Table 13. | 5IA-2322 / | TDA1541 | interconnection. |